*J. Basic. Appl. Sci. Res.*, 2(4)3476-3480, 2012 © 2012, TextRoad Publication ISSN 2090-4304 Journal of Basic and Applied Scientific Research www.textroad.com

# A 0.5-V 17- µW Second-Order Delta-Sigma Modulator Based on a Self-Biased Digital Inverter in 0.13µm CMOS

Ebrahim Abiri<sup>1\*</sup>, Nikta Pournoori<sup>2</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, Shiraz University of Technology, Shiraz, Iran. <sup>2</sup>Bushehr branch, Islamic Azad University, Bushehr, Iran.

# ABSTRACT

This paper proposes a self-biased digital inverter circuit and its application in a low power  $2^{nd}$  order switched-capacitor delta-sigma modulator. By employing the self-biasing technique, the gain performance of the modulator is improved and increased the power efficiency. The modulator is designed by using standard CMOS 0.13µm technology. The threshold voltages of the PMOS and NMOS transistors are 320mv and 380mv, respectively. All transistors are operated within the supply voltage 0.5 V. The designed modulator achieves 63.6dB Signal-to-noise ratio (SNR) and 63.6dB Signal-to-noise and distortion ratio (SNDR) in an input signal bandwidth of 8 KHz with a sampling frequency of 1.6 MHz. The modulator core consumes only  $4\mu$ W of power and the total power consumption is  $17\mu$ W. The proposed delta-sigma modulator achieves high power efficiency, low power, low voltage and high speed performances for practical applications.

KEY WORDS: Delta-Sigma Modulator. Self-Biased Digital Inverter. Low-Power. Low-Voltage.

### **1. INTRODUCTION**

The continuing CMOS technology scaling has enabled the digital systems by using a proportional reduction of the supply voltage to maintain the device's reliability and also decrease power consumption and lower costs. Therefore, the design of low power, low voltage and high speed analog circuits is always faced with challenges. In order to overcome these challenges several techniques have been investigated in many papers [1]-[8]. To design low voltage analog circuits, they use charge pumps [1], [2] switched-op amps [3], switched-RC [4] and the input-feed forward architecture [5]. A charge pumps technique generates higher voltage than the supply voltage for switches [1], [2]. To eliminate the need for charge pumps, switched-op amps technique with common mode level shift has been reported in [3]. Since switched-op amps circuits face a tradeoff between speed and accuracy, switched-RC technique which achieves high linearity and low-voltage operation are used in [4]. All above mentioned techniques may require extra control circuits and extra current which consumes more power and occupy the large area. To minimize the power consumption in a low-voltage environment, ultra-deep-submicron standard digital CMOS technologies are investigated [5] and also the input feed-forward architecture with the low-power operational transconductance amplifier (OTA) is proposed [6]. The supply voltages of the OTAs are confined and have reached the limits of further scaling, because they are strictly limited by the input common-mode voltage and they have complex circuitry to implement. Thus, to remove the need for OTAs, inverter-based amplifiers and self-biased fully differential super inverter has been reported recently [7], [8]. The most important reason using an inverter instead of amplifiers is simplicity and the capability of operating with ultra-low supply voltages [7]. The single-ended inverter utilized instead of an OTA in deltasigma modulator is replaced by the self-biased fully differential super inverter to increase its noise rejection which complicates the common-mode feedback design [8]. To improve the inverter's gain performance and attain higher power efficiency, low voltage, high speed and especially low power a self-biased digital inverter is presented and analyzed in this paper. By employing the self-biasing technique, the digital inverter enables circuit to be less sensitive to process, supply voltage and temperature (PVT) and parameter variations. In this case, the switching currents can be greater than the quiescent bias current. Also the external biasing voltages become unnecessary in this structure, thus saving power and die area. Therefore, the proposed self-biased digital inverter is suitable to use in switched-capacitor circuits for low power, low voltage and high speed. As a prototype, a low power second-order, single bit delta-sigma modulator based on a self-biased digital inverter is designed for practical applications. This paper is organized in the following manner. Section 2 describes the operation principle of a self-biased digital inverter. Section 3 discusses the details of the architectural delta-sigma modulator. Section 4 has simulation results, and section 5 provides conclusions.

Corresponding Author: Ebrahim Abiri, Department of Electrical and Electronics Engineering, Shiraz University of Technology, Shiraz, Iran. Email: abiri@sutech.ac.ir

#### Abiri and Pournoori 2012

# 2. SELF-BIASED DIGITAL INVERTER

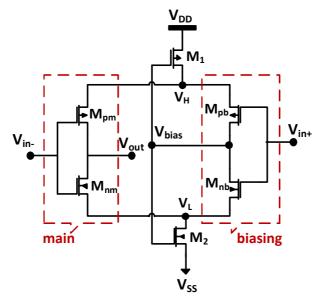

Instead of using self-biased super inverter structure that has been reported in [8], a self-biased digital inverter is proposed as illustrated in Fig.1. Compared to self-biased super inverter structure, the self-biased digital inverter structure not only achieves excellent power efficiency but also is compatible with very low voltage. Moreover, in this structure supplying switching currents can be much greater than the quiescent bias current which is one of the advantages for high speed and low power applications. One important design aspect in this structure is the size of transistor and the region of biasing. Thus, the transistors used in main inverter and biasing inverter should be biased in linear region and are equally sized. In order to have a circuit that can be compensate any PVT variation during circuit operation and stabilized the bias voltages,  $M_1$  and  $M_2$  are used in the negative feedback loop. In this case, transistors  $M_1$  and  $M_2$  are biased in linear region. Therefore, the  $V_H$  and  $V_L$  can be set very close to supply voltages. In fact, these two voltages determine the output swing which can be very close to difference between the two supply rails [9], [10]. The differential-mode gain ( $A_{dm}$ ) of the self-biased digital inverter is given by:

$$A_{dm} \cong \frac{g_{m1} + g_{m2}}{g_{out}} \tag{1}$$

Where  $g_{m1}$  and  $g_{m2}$  are the transconductances of transistors  $M_{pm-pb}$  and  $M_{nm-nb}$ , respectively and  $g_{out}$  is the output conductance of the self-biased digital inverter.

Fig.1. Circuit schematic of self-biased digital inverter

# 3. COMPLETE DELTA-SIGMA MODULATOR CIRCUIT

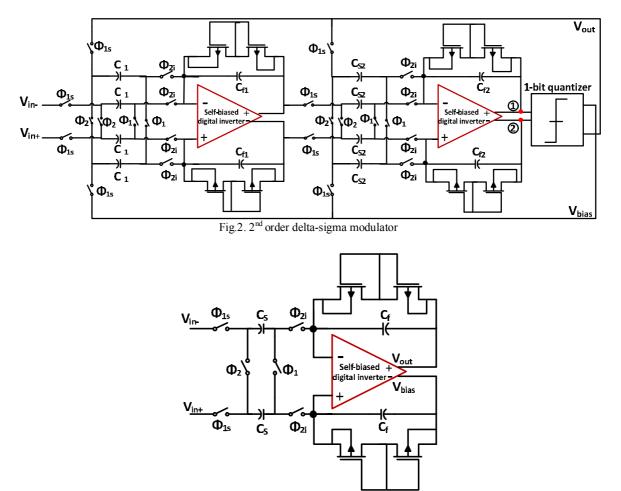

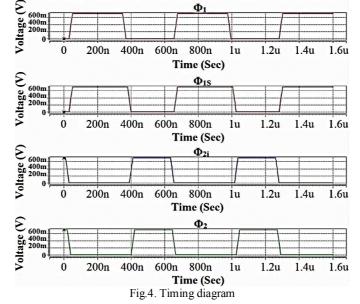

To design delta-sigma modulator circuit, several important criterions should be considered. The order of a modulator demonstrates the number of integrators. The choice between single loop and cascade architecture is a criterion should be noted. The choice between a single bit and multi bit quantizer that prepares B bits of resolution. The oversampling ratio is determined as the ratio of the modulator sampling rate to its Nyquist rate. The complete non cascaded 2<sup>nd</sup> order delta-sigma modulator circuit is shown in Fig.2. In this structure single loop architecture with a negative feedback, two integrators and a 1-bit quantizer is utilized. The self-biased digital inverter is used instead of externally-biased operational amplifiers in the switched-capacitor integrators for low-voltage low-power applications. To have high linearity performance a single bit quantizer is applied in the modulator. Since the key element in a delta-sigma modulator is the integrator, a switched-capacitor integrator incorporating the self-biased digital inverter operates with two phase clocks, sampling ( $\Phi_1 \& \Phi_{1s}$ ) and integration  $(\Phi_2 \& \Phi_{2i})$  phases, as illustrated in Fig.3. In the differential-mode operation, the input signal is sampled in the sampling capacitors (C<sub>s</sub>) during the sampling phase. In order to eliminate signal dependent charge injection, the  $\Phi_1$  is turning off slightly earlier than  $\Phi_{1s}$ . During integration phase,  $\Phi_{2i}$  is turning on slightly earlier than  $\Phi_2$  to shift the floating potential to common-mode voltage level. As soon as,  $\Phi_2$  switch is closed, the differential charges in sampling capacitors (C<sub>s</sub>) are transferred to the feedback capacitors ( $C_f$ ). Figure 4 shows the timing diagram of the non-overlapping clocks. All switches are NMOS only transistors and the input voltage amplitude of the clock generator is set to 0.7 V to ensure an adequately low switch resistance in a low supply voltage. The used sampling capacitors  $C_s$  in this integrator are completely matched and the capacitors values in this circuit are chosen as 100 pF. If the sampling capacitors values are less than 100 pF, the output voltage noise at the switched-capacitor integrator will be increased. In this structure, two anti-parallel PMOS transistors are

### J. Basic. Appl. Sci. Res., 2(4)3476-3480, 2012

connected in a negative feedback between the input and output ports of the self-biased digital inverter. These two PMOS transistors are equivalent two very large pseudo-resistors which balance the two common-mode voltages. Therefore, the differential gain does not decrease and occupy a smaller area than the resistor [8].

Fig.3. A switched-capacitor integrator incorporating the self-biased digital inverter

#### Abiri and Pournoori 2012

# 4. SIMULATION RESULTS

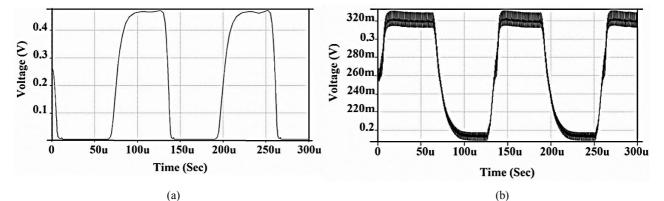

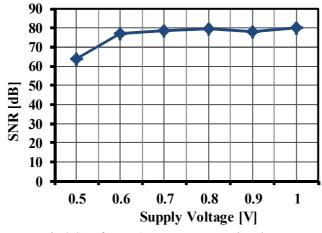

The proposed delta-sigma modulator is implemented in a 0.13 $\mu$ m CMOS technology. The design specifications of the modulator are summarized in Table 1. The simulated voltage waveforms at the output of the delta-sigma modulator (node 1 and node 2 in Fig.2.) for V<sub>dd</sub>=0.5 V are shown in Fig.5 (a), (b). Figure 6 shows the measured SNR for V<sub>in</sub>=1V<sub>P-P,diff</sub> versus supply voltage. The measured SNR and SNDR are 63.6dB and 63.6dB, respectively for an 8 KHz bandwidth with a 0.5 V supply voltage. Compared to a 2<sup>nd</sup> order delta-sigma modulator incorporating the self-biased super inverter which consumes 4.8 $\mu$ w of power in the core [8], the power consumption in the core of the proposed 2<sup>nd</sup> order delta-sigma modulator in this paper is only 4 $\mu$ W and the total power consumption including the clock generators is 17 $\mu$ W. The measurement of results at both 0.5 V and 1V power supplies are summarized in Table 2. The performance of our delta-sigma modulator is compared with other switched-capacitor delta-sigma modulators in Table 3. To compare the performances, the common figure-of-merit (FOM) equation [7] is utilized as follows:

$$FOM = \frac{Power}{2^{(SNDH[dc]-1./b]/bNZ} \times 2 \times BW}$$

(2)

Due to use a self-biased digital inverter, the presented modulator operates at the lowest voltage while maintaining an excellent FOM. Also, this modulator achieves an excellent performance in the power efficiency.

Fig.5. Simulated voltage waveforms at the output of the delta-sigma modulator for  $V_{dd}=0.5$  V: (a) Node 1 in Fig.2. (b) Node 2 in Fig.2.

Table 1. Design specifications of the modulator

| Technology               | 0.13µm CMOS          |                      |  |  |  |  |  |

|--------------------------|----------------------|----------------------|--|--|--|--|--|

| $(V_{TN}, V_{TP})$       | (380mV, 320mV)       |                      |  |  |  |  |  |

| Sampling Frequency       | 1.6 MHz              |                      |  |  |  |  |  |

| Input Bandwidth          | 8KHz                 |                      |  |  |  |  |  |

| Sampling Capacitors (pF) | C <sub>S1</sub> =100 | C <sub>S2</sub> =100 |  |  |  |  |  |

| Feedback Capacitors (pF) | C <sub>fl</sub> =0.8 | C <sub>f2</sub> =0.6 |  |  |  |  |  |

### J. Basic. Appl. Sci. Res., 2(4)3476-3480, 2012

| Table 2. Summary of simulation results |         |        |  |  |  |  |

|----------------------------------------|---------|--------|--|--|--|--|

| Supply Voltage                         | 0.5 V   | 1 V    |  |  |  |  |

| Peak SNR @8KHZ                         | 63.6 dB | 80 dB  |  |  |  |  |

| Peak SNDR @8KHZ                        | 63.6 dB | 80 dB  |  |  |  |  |

| Power Consumption in the core          | 4 μW    | 29.8mW |  |  |  |  |

| Total Power consumption                | 17µW    | 230mW  |  |  |  |  |

| FOM (pJ/Conversion step)               | 0.202   | 230    |  |  |  |  |

# Table 2. Summary of simulation results

### Table 3. Performance comparison of delta-sigma modulators

| Reference | Process<br>(μm) | BW<br>(KHz) | V <sub>dd</sub><br>(V) | power<br>(µW) | SNR<br>(dB) | FOM<br>(pJ/step) |

|-----------|-----------------|-------------|------------------------|---------------|-------------|------------------|

| [1]       | 0.35            | 25          | 1                      | 950           | 87          | 1.31             |

| [3]       | 0.18            | 8           | 0.7                    | 80            | 70 @ 2KHz   | 2.7              |

| [4]       | 0.35            | 24          | 0.6                    | 1000          | 77          | 3.6              |

| [5]       | 0.09            | 20          | 1                      | 140           | 85          | 0.38             |

| [6]       | 0.13            | 20          | 0.9                    | 60            | 82.2        | 0.406            |

| [7]*      | 0.35            | 8           | 1.2                    | 5.6           | 72          | 0.303            |

| [8]       | 0.13            | 8           | 1.2                    | 4.8           | 67 @ 2KHz   | 0.58             |

| This work | 0.13            | 8           | 0.5                    | 4             | 63.6        | 0.202            |

\* Modulator-II in [7] is used for comparison

## 5. CONCLUSION

A 0.5-V 17- $\mu$ w second-order delta-sigma modulator based on a self-biased digital inverter is realized in this paper. The prototype second-order delta-sigma modulator employing the self-biasing technique has been designed in 0.13 $\mu$ m CMOS technology using only standard V<sub>TH</sub> devices and consumes only 4 $\mu$ W of power in the core. The presented modulator achieves a peak SNR of 63.6dB over a signal bandwidth of 8 kHz with a sampling frequency of 1.6 MHz. The simulation results show that this modulator can be used for very low voltage and low power practical applications.

### REFRENCES

- Dessouky, M. and A. Kaiser, 2001. Very low-voltage digital-audio ∆∑ modulator with 88-dB dynamic range using local switch bootstrapping: IEEE J. Solid-State Circuits, 36 (3): 349-355.

- [2] Rabii, S. and B. A. Wooley, 1999. The Design of Low-Voltage, Low-Power Sigma-Delta Modulators. Norwell, MA: KAP.

- [3] Sauerbrey, J., T. Tille, D. Schmitt-Landsiedel and R. Thewes, 2002. A 0.7-V MOSFET-only switched-opamp  $\Delta \sum$  modulator in standard digital CMOS technology: IEEE J. Solid-State Circuits, 37: 1662-1669.

- [4] Ahn, G.-C., D.-Y. Chang, M. E. Brown, N. Ozaki, H. Youra, K.Yamamura, K. Hamashita, K. Takasuka, G. C. Temes, and U. Moon, 2005. A 0.6-V 82-dB delta-sigma audio ADC using switched-RC integrators: IEEE J. Solid-State Circuits, 40 (12): 2398-2407.

- [5] Yao, L., M. S. J. Steyaert, and W. Sansen, 2004. A 1-V 140-μW88-dB audio sigma-delta modulator in 90-nm CMOS: IEEE J. Solid-State Circuits, 39 (11): 1809-1818.

- [6] Roh, J., S. Byun, Y. Choi, H. Roh, Y.-G. Kim and J.-K. Kee, 2008. A 0.9-V 60-μW 1-bit fourth-order delta-sigma modulator with 83-dB dynamic range: IEEE J. Solid-State Circuits, 43(2): 361-370.

- [7] Youngchaeol, C. and H. Gunhee, 2009. Low voltage, low power, inverter-based switched-capacitor delta-sigma modulator: IEEE J. Solid-State Circuits, 44(2): 458-472.

- [8] Wang, L., L. Theogarajan, 2010. A Micropower Delta-Sigma Modulator based on a Self-Biased Super Inverter for Neural Recording Systems. In custom integrated circuits conference (CICC), pp: 1-4.

- [9] Figueiredo, M., T. Michalak, J. Goes, L. Gomes and P. Sniatala, 2009. Improved Clock-Phase Generator based on Self-biased CMOS Logic for Time-Interleaved SC circuits. In 16<sup>th</sup> IEEE International Conference, pp: 763-766.

- [10] Bazes, M., 1991. Two novel fully complementary self-biased CMOS differential amplifiers: IEEE J. Solid-State Circuits, 26(2): 165-168.